The tale of the Little Red Hen-gineer Pg 62

Boeing postpones test flights again: How's your tapeout looking? Pg 7

Signal Integrity: Shaping edges Pg 20

Design Ideas Pg 45

Supply Chain Pg 56

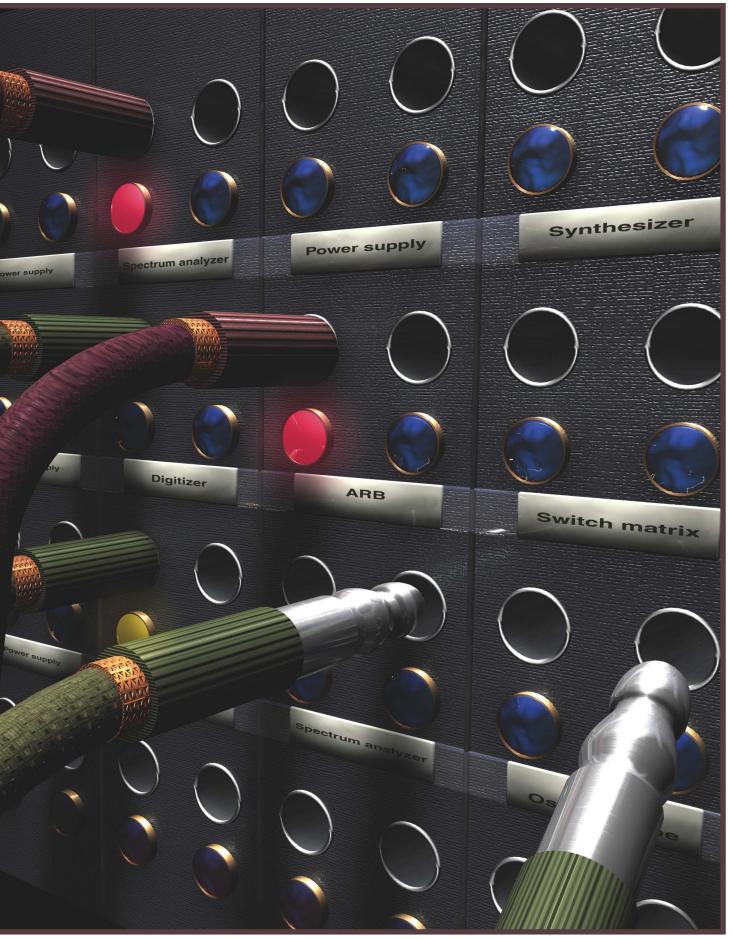

Power supply

ARB

### SMOOTH OPERATORS COMMUNICATING FOR COMMUNICATIONS TEST

Page 30

#### INDUSTRY STANDARDS LEAD PUSH TOWARD ENERGY-EFFICIENT COMPUTING

Page 25

# PCB-layout techniques for gigasample ADCs

Page 39

Digitizer

ectrum analyzer

#### High Fidelity Audio for: Automotive Consumer Professional

### Complex.

Simple.

# Finally! The All-In-One Audio IC

#### Designing Audio Systems Has Never Been Easier

The complex challenges of designing audio subsystems is a thing of the past. Cirrus Logic's **CS470XX** family combines an advanced 32-bit audio DSP, high performance multichannel audio codec, multichannel hardware sample rate converter and a digital audio receiver/transmitter into a single IC – without compromising analog performance.

With this unique all-in-one approach, you can eliminate complex schematics and painful debugging while dramatically reducing board space and system cost. Knock out those unnecessary components, speed up your design and crank up the sales.

#### **CS470XX FEATURES**

- 32-bit Audio DSP

- Hardware SRC

- 105 dB A/D Converters SPDIF Rx & Tx

Cirrus Logic. We make it easier for you.

- 108 dB D/A Converters

- 5:1 Analog Input MUX

- I<sup>2</sup>S I/O Support

Expansive Audio

- Processing Library

DSP COMPOSER™ Our easy-to-use drag-and-drop GUI tool makes DSP programming a breeze. Learn more at www.cirrus.com

**NORTH AMERICA** +1 800-625-4084

**ASIA PACIFIC** +852 2376-0801

JAPAN +81 (3) 5226-7757 EUROPE/UK +44 (0) 1628-891-300

To download the whitepaper Continuous-Time Converter Architectures for Integrated Audio Processors, visit www.cirrus.com/470XXedn

### LEARN MORE AT

© 2009 Cirrus Logic, Inc. All rights reserved. Cirrus Logic, Cirrus and the Cirrus Logic logo designs are trademarks of Cirrus Logic, Inc. All other brands and product names may be trademarks or service marks of their respective owners. EDN1122009

# WHERE DESIGN ENGINEERS GO FIRST! DIGIKEY.COM

<u> Jiqi-Ke</u>

INE ORDERING

ORDER STATUS Roduct inde)

CONTACT US

SITE MAP About Digi-Key

#1 Breadth of Product Line#1 Availability of Product#1 Overall Performance

Source: **EE**Times Distribution Study, August 2008

IVQ-IXEN

The industry's broadest product selection available for immediate delivery

CORPORATION

1

### www.digikey.com 1.800.344.4539

Digi-Key is an authorized distributor for all supplier partners. New products added daily. © 2009 Digi-Key Corporation, 701 Brooks Ave. South, Thief River Falls, MN 56701, USA

1-800-344-4530

? Nee

000

30

PRODUCTS

000

ADDED 90 DAYS!

WHAT'S NEW

# Test. Accelerated.

Reduce Your Cost with a Faster Automated Test System

#### PRODUCT PLATFORM

NI TestStand software NI LabVIEW graphical software PXI modular instrumentation For more than 30 years, National Instruments technology has been the foundation for building faster automated test and measurement systems. The NI test platform combines the advantages of open PC-based systems, PXI modular instrumentation, and unlimited instrument control solutions – all powered by the industry's most comprehensive and widely chosen test system software.

>> Learn best practices for test system design at ni.com/automatedtest

#### 800 891 8841

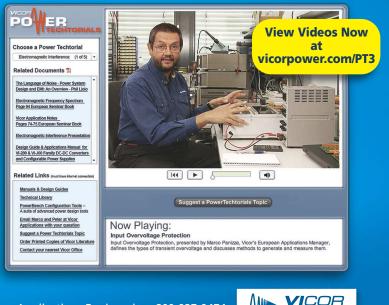

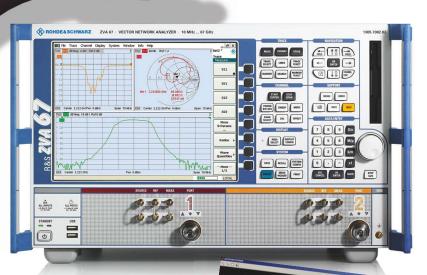

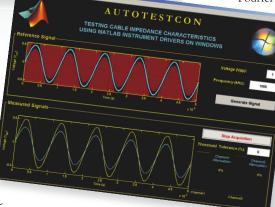

#### Smooth operators: communicating for communications test

BOCKET Control Control

# Dilbert 12

- 11 FPGA evaluation boards come with design software

- 12 Signal analyzers outshine spectrum-analyzer cousins

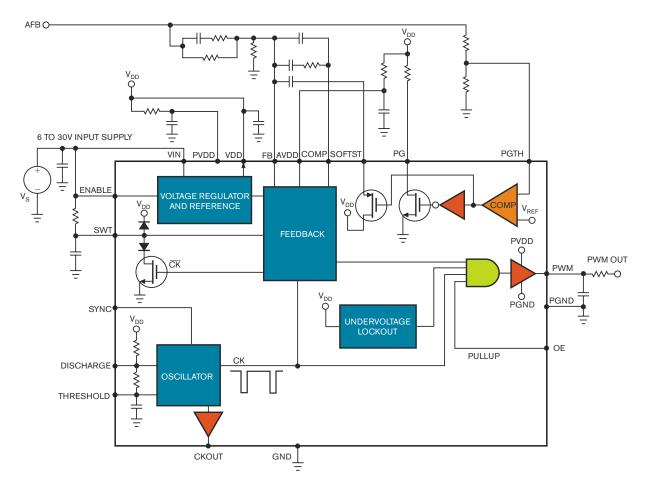

- 14 PWM-controller IC operates at temperatures as high as 225°C

- 16 Device enables remote computer control and management

- 16 Avnet releases Xilinx Spartan-6 FPGA evaluation and development kits

- 19 **Research Update:** Team hardens SiGe circuits; Digital photomultipliers challenge vacuum-tube photomultipliers

#### Industry standards lead push toward energy-efficient computing

25 Environmental concerns and rising energy costs are spurring the development of requirements for high-efficiency ac and dc power conversion. Meeting the newest specifications will demand knowledge of competing power-conversion topologies, components, and design.

> by Lee Harrison, Peritus Power

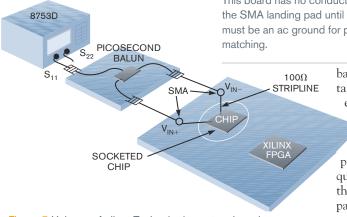

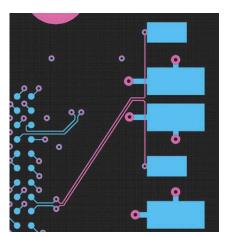

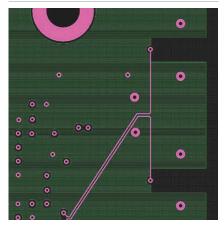

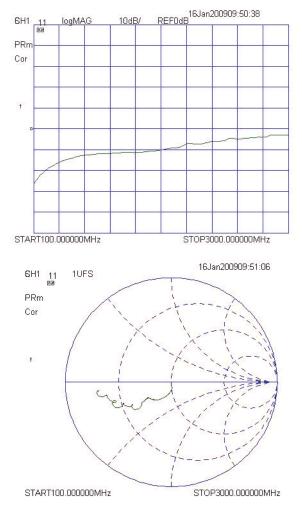

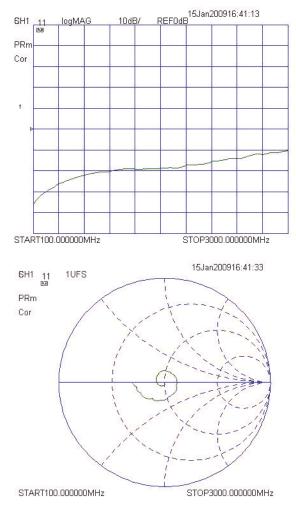

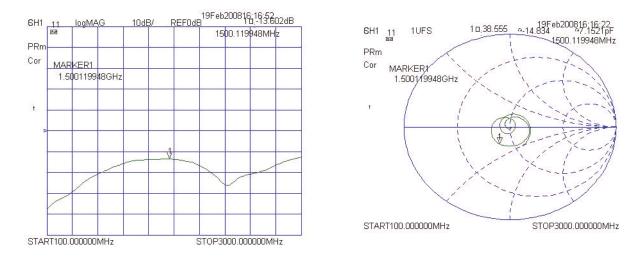

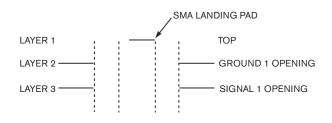

# PCB-layout techniques for gigasample ADCs

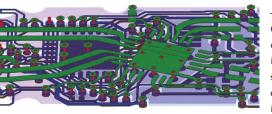

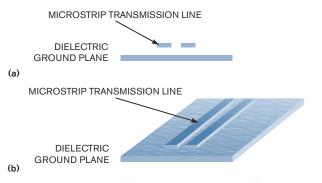

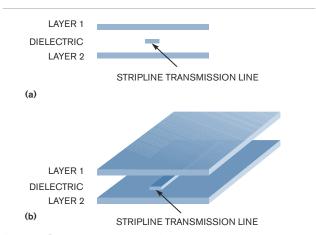

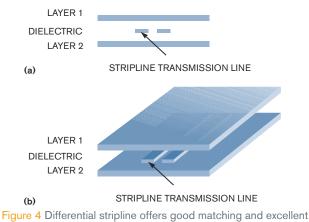

**39**When a multilayer board operates at speeds greater than a few hundred megahertz, it's a challenge to maintain signals without mismatches, losses, distortion, or EMI. Follow these guidelines for PCB layout to preserve signal integrity and achieve high-speed performance.

> by Edison Fong, National Semiconductor

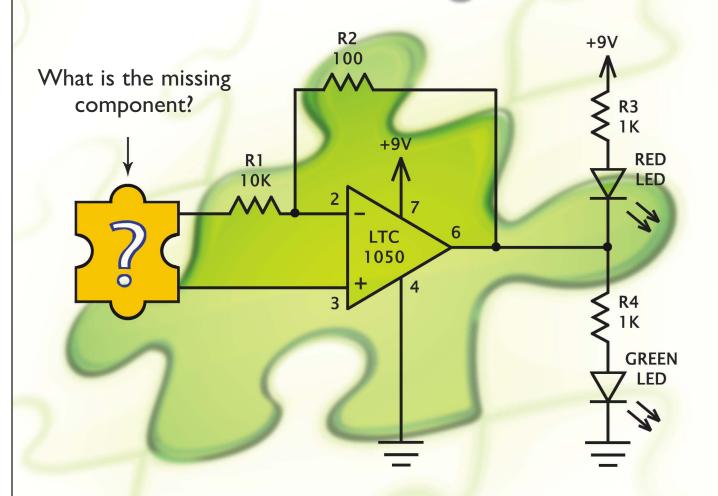

# DESIGNIDEAS

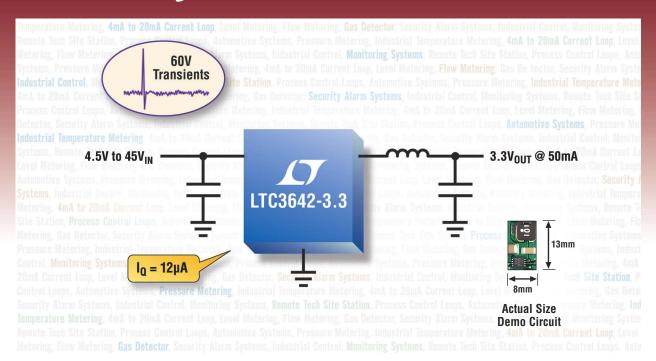

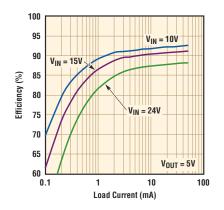

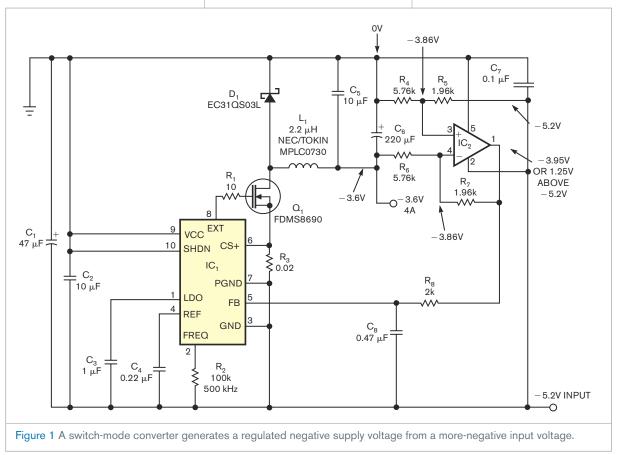

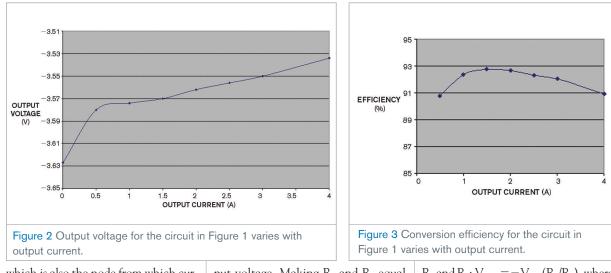

45 Negative-to-negative switch-mode converter offers high current and high efficiency

EDN 11.12.09 contents

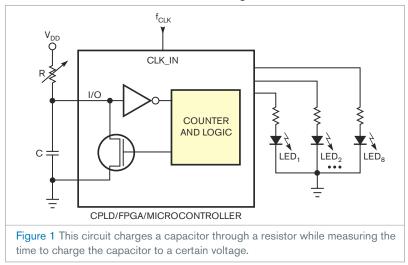

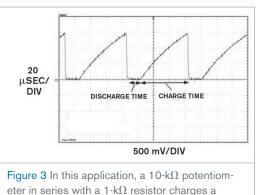

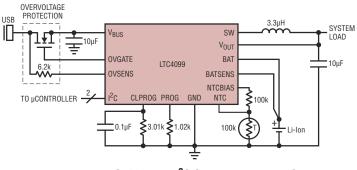

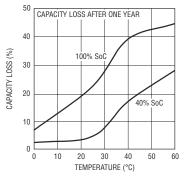

46 ADC for programmable logic uses one capacitor

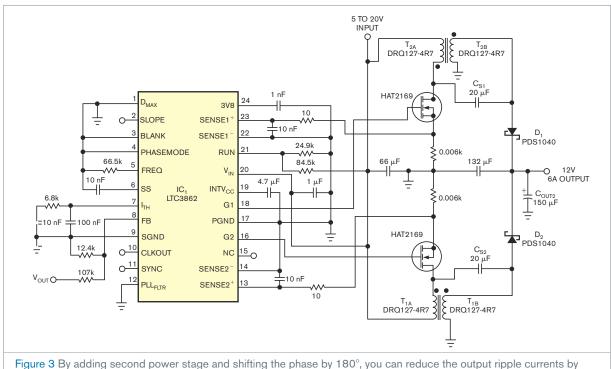

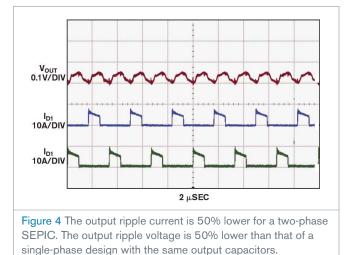

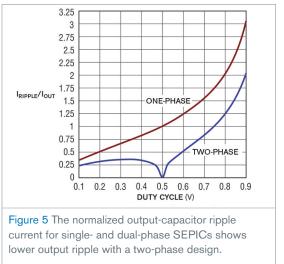

51 Use two phases to cut current and improve EMI

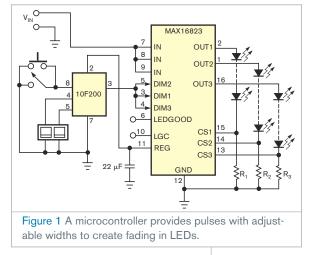

52 Fader switch uses inexpensive controller

#### More measurements. More data. Less cost.

With up to 560 channels of data logging at a maximum scan rate of 1000 channels/sec, an internal 6 ½ digit DMM with 22-bit resolution, and 0.03% accuracy, it's no mystery why Agilent's data acquisition systems are among the top selling in the world. The 34970A and 34980A are both at home with either data acquisition or functional test,

with a broad selection of plug-in modules. Now with Agilent Data Logger Pro software, you'll be able to collect data, check limits, perform extensive branching, and view and store the data without authoring the programming yourself. It's an ideal expansion at a significant savings.

#### www.agilent.com/find/daqswitch

Agilent Authorized Distributor

Newark

800-463-9275 www.newark.com/agilent

# contents 11.12.09

### **DEPARTMENTS & COLUMNS**

- 7 **EDN.comment:** Boeing postpones test flights again: How's your tapeout looking?

- 20 Signal Integrity: Shaping edges

- 22 Tapeout: Reference-tool flows and process-design kits, part two

- 56 **Supply Chain:** Outsourcing to China in question; BLE set for surge; MIIT proposes China ROHS catalog

- 59 Product Roundup: Discrete Semiconductors, Integrated Circuits

- 62 **Tales from the Cube:** "Not I," said the rat: the tale of the Little Red Hen-gineer

### **EDN** online contents

www.edn.com

#### ONLINE ONLY

Check out this Web-exclusive article:

Implementing an all-digital PHY and DLL for high-speed DDR2/3 memory interfaces A new, all-digital approach to implementing high-speed PHY (physical-layer) logic and a DLL (delay-locked loop) offers a path to addressing increasingly stringent market requirements.

→www.edn.com/article/CA6701965

#### Power Leaders: ICs & Solar

This special section takes a look at the leading vendors in the semiconductor industry for power transistors and diodes, powermanagement ICs, digital power, and photovoltaics. →www.edn.com/info/ CA6703024.html

### INNO ATION WANTED NOW!

We're accepting nominations for the 20th annual Innovation Awards, which will take place in April 2010.

Don't miss this opportunity for your company's and colleagues' accomplishments to be recognized. The official call for nominations, including complete information and step-by-step instructions, is posted at:

www.edn.com/innovation

EDN ® (ISSN#0012-7515), (GST#123397457) is published biweekly, 24 times per year, by Reed Business Information, 8878 Barrons Blvd, Highlands Ranch, CO 80129-2345. Reed Business Information, a division of Reed Elsevier Inc, is located at 360 Park Avenue South, New York, NY 10010. John Poulin, CEO/CFO, RBI-US; Jeff DeBalko, President, Business Media. Periodicals postage paid at Littleton, CO 80129-345. Telephone (303) 470-4445. Circulation records are maintained at Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN®, PO Box 7500, Highlands Ranch, CO 80163-7500, EDN & copyright 2009 by Reed Elsevier Inc. Rates for nonqualified subscriptions, including all issues: US, \$179.99 one year; Canada, \$229.99 one year (arexpedited, \$399.99 one year), arexpedited, \$399.99 one year. Servent for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. Publications Agreement No. 40685520. Return undeliverable Canadian addresses to: RCS International, Box 697 STN A, Windsor Ontario NSA 6N4. E-mail: Subsmail@ReedBusiness.com. Please address all subscription mail to EDN®, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. EDN® is a registered trademark of Reed Elsevier Properties Inc, used under license. A Reed Business Information Publication/Volume 54, Number 21 (Pinited in USA).

### Simpler Power Conversion

IR's AC-DC product portfolio offers simple, compact high density solutions tailored for energy-efficient power supplies.

#### µPFC™ PFC IC

| Part<br>Number     | Pckg.         | V <sub>cc</sub><br>(V) | Freq.<br>(kHz) | Gate<br>Drive<br>±(A) | V <sub>GATE</sub><br>Clamp<br>(V) | Current<br>Mode |

|--------------------|---------------|------------------------|----------------|-----------------------|-----------------------------------|-----------------|

| IR1150<br>(STR)PbF | SO-8<br>PDIP8 | 13-22                  | 50-200         | 1.5                   |                                   | ССМ             |

|                    |               |                        |                |                       |                                   |                 |

#### SmartRectifier<sup>™</sup> IC

| Part<br>Number                 | IR1166S<br>PbF | IR1167AS<br>PbF | IR1167BS<br>PbF | IR1168S<br>PbF |  |  |  |  |  |  |

|--------------------------------|----------------|-----------------|-----------------|----------------|--|--|--|--|--|--|

| Package                        | S0-8           |                 |                 |                |  |  |  |  |  |  |

| V <sub>cc</sub> (V)            |                | 20              |                 |                |  |  |  |  |  |  |

| V <sub>fet</sub> (V)           |                |                 | =200            |                |  |  |  |  |  |  |

| Sw Freq.<br>max (kHz)          | 500            |                 |                 |                |  |  |  |  |  |  |

| Gate Drive<br>±(A)             | +1/-4          | +2              | +1/-4           |                |  |  |  |  |  |  |

| V <sub>gate</sub> Clamp<br>(V) | 10.7           | 10.7            | 14.5            | 10.7           |  |  |  |  |  |  |

| Min. On Time<br>(ns)           | P              | 750             |                 |                |  |  |  |  |  |  |

| Channel                        |                | 1 2             |                 |                |  |  |  |  |  |  |

| RoHS                           | v              |                 | v v             |                |  |  |  |  |  |  |

For more information call 1.800.981.8699 or visit

International **ICR** Rectifier THE POWER MANAGEMENT LEADER

2500 Std. Models Surface Mount and Thru-Hole

#### **DC-DC Converters** 2 to 10,000 VDC Outputs

Low Profile / Isolated Up to 10,000 Volts Standard Regulated Models Available

INDUSTRIAL • COTS • MILITARY Delivery Stock to ONE WEEK

PICO ELECTRONICS, Inc. 143 Sparks Ave., Pelham, New York 10803 See EEM or send direct for Free PICO Catalog Call Toll Free 800-431-1064 • FAX 914-738-8225 E Mail: info@picoelectronics.com

PRESIDENT, BUSINESS MEDIA, REED BUSINESS INFORMATION

Jeff DeBalko, jeff.debalko@reedbusiness.com 1-646-746-6573

PUBLISHER, EDN WORLDWIDE Russell E Pratt

1-781-734-8417; rpratt@reedbusiness.com

ASSOCIATE PUBLISHER, EDN WORLDWIDE Judy Hayes 1-925-736-7617; judy.hayes@reedbusiness.com

VICE PRESIDENT, INTERACTIVE MEDIA AND SALES MANAGEMENT Karthik Krishnan 1-646-746-7580; karthik krishnan@reedbusiness.com

EDITOR-IN-CHIEF, EDN WORLDWIDE

Rick Nelson 1-781-734-8418; rnelson@reedbusiness.com

EXECUTIVE EDITOR Ron Wilson 1-510-744-1263; ronald.wilson@reedbusiness.com

MANAGING EDITOR Amy Norcross 1-781-734-8436; fax: 1-720-356-9161; amy.norcross@reedbusiness.com Contact for contributed technical articles

SENIOR ART DIRECTOR Mike O'Leary 1-781-734-8307; fax: 1-303-265-3021; moleary@reedbusiness.com

ANALOG Paul Rako, Technical Editor 1-408-745-1994; paul.rako@edn.com

MASS STORAGE, MULTIMEDIA, PCs, AND PERIPHERALS Brian Dipert, Senior Technical Editor 1-916-760-0159; fax: 1-303-265-3187; bdipert@edn.com

MICROPROCESSORS, DSPs, AND TOOLS Robert Cravotta, Technical Editor 1-661-296-5096; fax: 1-303-265-3116; rcravotta@edn.com

> NEWS Suzanne Deffree, Managing Editor 1-631-266-3433; sdeffree@reedbusiness.com

POWER SOURCES, ONLINE INITIATIVES Margery Conner, Technical Editor 1-805-461-8242; fax: 1-805-461-9640; mconner@reedbusiness.com

DESIGN IDEAS EDITOR Martin Rowe, Senior Technical Editor, Test & Measurement World edndesignideas@reedbusiness.com

EDN. 225 Wyman St, Waltham, MA 02451. www.edn.com. Phone 1-781-734-8000. Address changes or subscription inquiries: phone 1-800-446-6551; fax 1-303-470-4280; subsmail@ reedbusiness.com. For a free subscription, go to www.geffreemag.com/edn. Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Include your mailing label.

**Reed Electronics Group**

SENIOR ASSOCIATE EDITOR

Frances T Granville 1-781-734-8439; fax: 1-303-265-3131; f.granville@reedbusiness.com

EDITORIAL/WEB PRODUCTION Diane Malone Manager 1-781-734-8445; fax: 1-303-265-3024 Steve Mahoney Production/Editorial Coordinator 1-781-734-8442; fax: 1-303-265-3198 Melissa Annand Web Operations Specialist 1-781-734-8443; fax: 1-303-265-3279 Adam Odoardi Prepress Manager 1-781-734-8325; fax: 1-303-265-3042

> CONSULTING EDITOR Jim Williams, Staff Scientist, Linear Technology

CONTRIBUTING TECHNICAL EDITORS Dan Strassberg, strassbergedn@att.net Nicholas Cravotta, editor@nicholascravotta.com

COLUMNISTS Howard Johnson, PhD, Signal Consulting Bonnie Baker, Texas Instruments Pallab Chatterjee, SiliconMap

PRODUCTION Dorothy Buchholz, Group Production Director 1-781-734-8329 Joshua S Levin-Epstein, Production Manager 1-781-734-8333; fax: 1-781-734-8096

EDN EUROPE Graham Prophet, Editor, Reed Publishing +44 118 935 1650; gprophet@reedbusiness.com

EDN ASIA Luke Rattigan, Chief Executive Officer luke.rattigan@rbi-asia.com Kirtimaya Varma, Editor-in-Chief kirti.varma@rbi-asia.com

**EDN CHINA** William Zhang, Publisher and Editorial Director wmzhang@rbichina.com.cn Jeff Lu, Executive Editor jefflu@rbichina.com.cn

> EDN JAPAN Katsuya Watanabe, Publisher k.watanabe@reedbusiness.jp Ken Amemoto, Editor-in-Chief amemoto@reedbusiness.jp

# **Final State**

#### BY RON WILSON, EXECUTIVE EDITOR

### Boeing postpones test flights again: How's your tapeout looking?

oeing—giant aircraft manufacturer, equally giant but much-lower-profile defense contractor, and one-time paragon of complex project management—has hit the newspapers twice in recent weeks in the worst possible way. The company has announced that it is taking financial charges because neither of its two premier commercial projects—

the 787 Dreamliner and the 747-8 cargo version—will meet its most recent schedule for a first test flight. This concern directly affects suppliers

providing electronics to those programs. But it is also a cautionary tale for any chip-design team engaged in a complex project.

The irony is that this scenario should happen to Boeing. In the late 1960s, Boeing astonished the aircraft industry by creating the most complex jetliner to date-the initial 747-on a tight schedule and at enormous risk. The company bet essentially its net worth on the 747 project-on a schedule so tight that the first planes for delivery were on the running production line right behind the plane for flight testing and FAA (Federal Aviation Administration) certification. If something had gone seriously wrong, Boeing might have had to rework a year's worth of deliveries in parallel on the factory floor. But the plan-and the planeworked. The 747 project became a case study in project management and forever altered the landscape of the commercial-aviation market.

That scenario happened when there was limited use of computers and engineers learned manual project-management skills over decades in the must-do environments of World War II, the Cold War, and the Apollo program. Boeing's current disaster is taking place in an environment in which computers control everything. The managers supervising these projects typically have proven expertise in getting a master's degree in business administration, not in getting a project out the door. And this era is one of outsourcing.

According to published reports, these changes lie at the heart of Boeing's problems. To paraphrase one report, the 787 is an entirely modularized design, and Boeing outsourced the modules. The company intended that final assembly would comprise simply snapping together functionally complete modules, carrying the necessary electronic subsystems, cabling, plumbing, and mechanicals. When the modules started arriving, however, Boeing found that it had somehow lost control of the module designs. In some cases, things didn't fit. In others, module designs exceeded the capabilities of the subcontractors, and so the modules arrived with subsystems missing. Modules required further assembly after delivery. Perhaps more disturbing, no one had, at a full-system level, reality-tested software simulations of the system-level mechanical behavior of the composite materials of which the modules were constructed.

By now, I'm sure this scenario is beginning to sound relevant to chip-design managers. We, too, live in a world of pervasive outsourcing, increasing dependence on simulation at several unlinked levels of abstraction, and no chance of a reality check until someone assembles the complete system. We, too, live in the shadow of the possibility that a system-level design error will become visible only when we flatten the design for physical extraction and DRC (design-rule checking) or during silicon debugging.

In some ways, our problem is more controllable. There are fewer degrees of freedom in even a challenging mixed-signal block than in a physical chunk of a jumbo jet. We have put a lot of investment into tools to manage those degrees of freedom we must accept. And unlike Boeing, no chip-design team is the only one doing what it is doing. (Intel's R&D people are welcome to dispute this point.) So there is a body of experience, however imperfectly we share it.

Yet the caution is still there. It takes only a bit too much confidence in the tools and abstractions; just a little too much casual dealing with the company, language, and time barriers between the core team and the subcontractors; and one step too far down the path of partitioning to turn a challenging project into a catastrophe. The realities of mechanical design and the needs of Boeing's customers place limitations on that company's ambitions. But unlike Boeing, IC-design engineers are all servants of never-ceasing Moore's Law. To

paraphrase Intel, only the paranoid are likely to survive.**EDN**

Contact me at ronald.wilson@ reedbusiness.com.

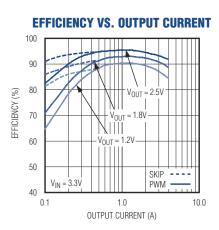

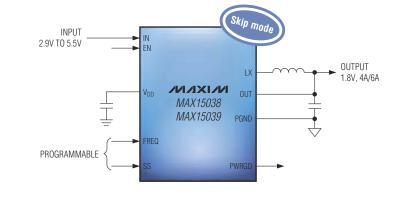

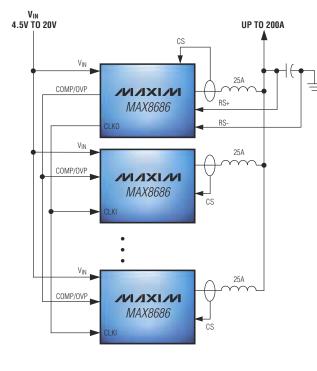

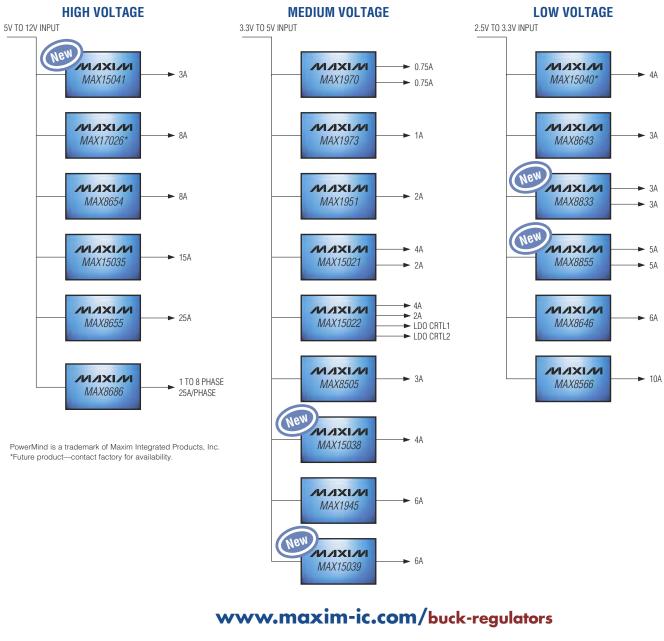

# Buck regulators with integrated MOS FETs simplify designs up to 25A/phase

### **High efficiency**

### 1- to 8-phase buck regulator with 25A/phase in a 6mm x 6mm TQFN

- 4.5V to 20V input voltage supply

- ±1% reference voltage accuracy over temperature

- Reference input (REFIN) for output tracking or system reference voltage

- Adjustable switching frequency from 300kHz to 1MHz

- Output sink and source current capability

Maxim's PowerMind<sup>TM</sup> family of integrated buck regulators simplifies your toughest design challenges. These regulators provide high efficiency in compact, simple, cost-effective solutions that have the industry's lowest EMÍ.

www.maxim-ic.com/shop www.em.avnet.com/maxim

Innovation Delivered is a trademark and Maxim is a registered trademark of Maxim Integrated Products, Inc. @ 2009 Maxim Integrated Products, Inc. All rights reserved.

#### For free samples or technical support, visit our website.

## MEET THE GUY that ELIMINATED HIS TEAM'S MANUFACTURING VARIABILITY ISSUES.

FIX YOUR MANUFACTURING VARIABILITY PROBLEMS AND YOUR REPUTATION WILL PRECEDE YOU. If you're designing chips for high functionality, high speed and lower power consumption at the most advanced process nodes, you've got variability issues. We have the solution that will increase your yield, performance and prestige by a wide margin. | Get more information at mentor.com/solutions/manufacturing-variability.

# EDITED BY FRAN GRANVILLE STATE OF THE OWNER OWNER OF THE OWNER OW

# FPGA evaluation boards come with design software

Itium's new NanoBoard 3000 embedded-system development platform includes a board with an FPGA chip. an IR (infrared) remote control, and a 12month license for Altium Designer schematic and FPGA software. Boards are available for Altera (www.altera.com) Cyclone III, Lattice (www.latticesemi.com) ECP2, and Xilinx (www. xilinx.com) Spartan-3AN FPGAs. The boards come with royalty-free IP (intellectual property) for functions such as a USB (Universal Serial Bus) interface, a TCP/IP (Transmission Control Protocol/Internet Protocol) stack, a touchscreen, a PS2 controller, and SVGA (super-video-graphics-array) capability. The units include three USB ports; an SVGA Dsub connection; eight RGB (red/green/blue) LEDs; and a 2.4-in., 320×230-pixel LCD with touchscreen.

Audio features include a stereo-digital-audio system with onboard power amplifiers and speakers, along with a MIDI (musical-instrument-digital-interface) connector set. Four relays and four PWM (pulse-width-modulated) power drivers provide power management and motion control. Headers bring out 36 digital-I/O pins from the FPGA, and a connector provides access to 50 digital I/Os and to the audio system and power rails. An RJ-45 connecter provides either 10BaseT or 100BaseTX Ethernet connections. An IR receiver lets you provide command input

from the remote-control unit. Other features include an SD (secure-digital)-Card reader; PS2 ports for keyboard and mouse; two connectors for RS-232 and RS-485 ports; a fourchannel, 8-bit ADC; and a four-channel, 8-bit DAC.

Altium is developing a wireless peripheraladd-on board, for release in December, that supports GSM (global system for mobile) communications, GPS (global-positioning system), and Bluetooth. The Xilinx Spartan-3AN NanoBoard is available now. The Altera Cyclone III and the Lattice ECP2 boards will be available in December. They sell for \$395 each, including software, a desktop stand, a speaker-board subassembly, a power-supply module, four power cords for worldwide outlets, a USB cable, an IR remote-control unit with two AAA batteries, an LCD stylus, four jumpers, a volume knob, and an LCDcleaning cloth. An external enclosure (http:// wiki.altium.com/display/ADOH/NanoBoard +3000+Modular+Enclosure) is available for \$129.-by Paul Rako

►**Altium**, http://wiki.altium.com/display/ ADOH/NanoBoard+3000+Series.

and a

#### FEEDBACK LOOP

The only reason we're embroiled in this stupid mess is because the (former Federal Communications **Commission Chairman** Michael) Powell FCC destroyed the common-carrier model, which works so well in the rest of the world. But for that ruling, which gave a monopoly on Internet provisioning to a handful of telephone companies, just because they owned some poles at the side of the road and the metro-cable plant, we wouldn't need to be arguing about 'neutrality.'"

—Reader "Scunnerous," in *EDN*'s Feedback Loop, at www.edn. com/article/CA6699736. Add your comments.

The Altium NanoBoard 3000 includes hardware, software, and IP blocks to help you design a sophisticated FPGA system.

# pulse

# Signal analyzers outshine spectrum-analyzer cousins

gilent's new N9000A CXA and N9030A PXA series of signal analyzers target a wider niche than do swept-frequency spectrum analyzers. The low-cost N9000A CXA has bandwidths as high as 7.5 GHz, and the high-performance N9030A PXA has bandwidths as high as 26.5 GHz. They offer an array of built-in and optional capabilities that enable them to also perform many tasks that have become critical in testing and evaluating today's complex, digitally modulated communications signals. Both series are part of the manufacturer's larger X-Series, which also includes the EXA and MXA series.

The CXA series' 3- and 7.5-GHz units, whose US base prices range from \$12,657 to approximately \$16,360, target general-purpose electronics manufacturing, low-cost R&D, and RF education, for which they provide flexibility through built-in and optional measurement capabilities that you can easily reconfigure. The PXA series' architecture supports new measurement applications; future hardware add-ons; wider analysis bandwidths; and possible upgrades to the instrument CPU, memory, disk drives, and I/O ports. The series' models cover frequency ranges of 3

Thanks to many built-in and optional features, low-cost CXA and high-performance PXA signal analyzers are more than just sweptfrequency spectrum analyzers.

#### The PXA is a form, fit, and function replacement for several popular spectrum analyzers.

to 3.6, 8.4, 13.6, and 26.5 GHz, and base prices range from \$51,900 to \$66,300.

CXA analyzers offer built-in one-button measurements and optional advanced-measurement applications, including preconfigured test routines for noise figure, phase noise, and analog demodulation. To ensure consistency, the applications are virtually identical to those that run on the EXA, MXA, and PXA analyzers. In addition, the manufacturer's 89600 VSA (vector-signal-analysis) software can run inside the Windows-based instrument, providing advanced analysis of more than 50 demodulation formats. On the production line, the CXA is more than two times as fast as other low-cost analyzers. For example, the CXA can return a peak search result in less than 5 msec and perform a remote sweep and transfer in less than 12 msec through IEEE 488.

The units also include LAN and USB (Universal Serial Bus) 2.0 interfaces. Switching between measurement modes typically takes less than 75 msec. The CXA series offers  $\pm$ 0.5-dB absolute amplitude accuracy, 13-dBm TOI (thirdorder intermodulation), -157dBm DANL (displayed average-noise level), and 65-dB-WCDMA (wideband-code-division-multiple-access) ACLR (adjacent-channel-leakage-

power-ratio) dynamic range. PXA units reduce measurement uncertainty and reveal new levels of signal detail, starting with spurious-free dynamic range as great as 75 dB with 140-MHz analysis bandwidth. Other specifications include -128-dBc/Hz phase noise at 1 GHz with 10-kHz offset, 0.19-dB absolute amplitude inaccuracy, and -172dBm DANL-based sensitivity at 2 GHz, with preamplifier and noise-floor-extension technology. Like the CXA series, the PXA series offers built-in onebutton measurements, optional advanced-measurement applications, and compatibility with other X-Series analyzers and with the manufacturer's 89600 VSA software.

For those looking to easily refresh or replace their test systems, the PXA is a form, fit, and function replacement for several popular spectrum analyzers, including the HP 8566 and 8568; HP/Agilent 856x; and Agilent PSA units whose bandwidth extends to 26.5 GHz. Key features include code compatibility; emulation of remote-programming language; default settings, timings, and couplings; arbitrary and second-IF output; fastrise-time logarithmic-video output; and Y-axis output. You can purchase The MathWorks' (www.mathworks.com) Matlab data-analysis software directly from Agilent as an option on all X-Series signal analyzers. These packages enable you to make application-specific measurements and test-modulation schemes and to develop customized applications.

#### −by Dan Strassberg ▶Agilent Technologies,

www.agilent.com/find/CXA, www.agilent.com/find/PXA, www.agilent.com/find/ X-Series\_backgrounder.

#### RAQ's

# **Rarely Asked Questions**

Strange stories from the call logs of Analog Devices

### Bring on the Converter Noise! – Part 1

# **Q.** Is Noise Figure important from the A/D converter's perspective?

**A.** In terms of the converter, noise figure (NF) and signal-to-noise ratio (SNR) are interchangeable. NF is great for understanding noise density, while SNR measures the total amount of noise in the band of interest. Let's take a closer look at NF though. Some tradeoffs can be misleading, and low NF does not always translate into lower front-end noise seen by the converter.

NF is easy to use in cascaded signal chains when trying to understand the dynamic implications of the design. Remember, that as the source resistance is quadrupled, the NF will improve by 6 dB, but the increased resistance will also increase the Johnson noise that will be seen by the converter. With more source resistance, or half of the full-scale input signal across the converter's analog frontend (transformer, amplifier, or otherwise), noise becomes more difficult to manage over the band of interest, ultimately making the converter's performance worse.

Why is this? If the full-scale input to the transformer or amplifier is lowered, the gain must be increased. This looks fine on paper, for transformers they are more gain-bandwidth dependent than amplifiers. Therefore, optimizing the NF to be as low as possible using a high-impedance ratio transformer, for example, makes it difficult to realize common high-IF applications of 100 MHz and above.

The problem with amplifiers is similar: as the gain of the amplifier is increased the amplifier not only amplifies the signal, it also amplifies its own inherent noise, thus

rapidly degrading the converter's performance. In order to preserve performance, a more complicated (higher order) antialiasing filter is required, making it rich with resistive and "lossy" components.

When designing a front-end, keep noise spectral density (NSD) in mind instead. Usually specified in nV/rt-Hz, this is what's really important to the converter, as this is what will be reported and crunched in the digital domain in order to differentiate and ultimately "pick out" the signals of interest within band.

In summary, make sure all the input and output full-scale signals are maximized throughout the signal chain by positioning gain where appropriate. Attenuation, padding, or resistance is not a good NF tradeoff in any signal chain, as it wastes power and increases noise due to resistors. Part 2 will discuss the comparison between resistor noise and converter noise.

A/D Converter Noise Figure equation: NF = Pfs(dBm) + 174dBm - SNR - 10\*log(BW). Where Pfs = the fullscale power of the input network used.

To Learn More About the Importance of ADC Noise Figure http://designnews.hotims.com/23125-101

**Contributing Writer Rob Reeder is a senior** converter applications engineer working in **Analog Devices high**speed converter group in Greensboro. NC since 1998. Rob received his MSEE and BSEE from Northern Illinois University in DeKalb, IL in 1998 and 1996 respectively. In his spare time he enjoys mixing music, art, and playing basketball with his two boys.

Have a question involving a perplexing or unusual analog problem? Submit your question to: raq@reedbusiness.com

For Analog Devices' Technical Support, Call 800-AnalogD

SPONSORED BY

# pulse

# PWM-controller IC operates at temperatures as high as 225°C

issoid has introduced the Magma switchingpower-supply PWM (pulse-width-modulator)-controller chip, which operates with 6 to 30V inputs and provides duty cycles up to 90%. The device operates at -55to  $+225^{\circ}$ C, and shutdown current is less than 150  $\mu$ A at 225°C. You can synchronize the chip to an external clock, and a clock-output pin makes the internal clock available.

Other features include an internal reference, input-voltage feedforward, and a softstart function when the device

The ceramic package of the Magma PWM-control chip allows it to operate over a -55 to  $+225^{\circ}$ C temperature range.

comes out of standby or when you enable the outputs. You can adjust the voltage threshold of the power-good output pin.

The device works with the

company's Hyperion transistor-driver chip, which also operates at 225°C. This chip set can drive high-temperature silicon-carbide transistors, FETs, or high-reliability IGBTs (insulated-gate bipolar transistors). The parts complement Cissoid's line of regulators, amplifiers, ADCs, logic, and P- and N-channel FETs, all of which operate at temperatures as high as 225°C.

Magma provides PWM control for down-hole oil-well instrumentation, aeronautics, train, and automotive applications. It comes in a ceramic DIL-28 package and sells for \$312.70 (200).

#### -by Paul Rako

Cissoid, www.cissoid.com.

You can use the high-temperature Magma PWM controller to make regulators and battery chargers that operate at 225°C.

### **Powerful, Versatile and Affordable...** 100 kHz Dynamic Signal Analyzer

- DC to 100 kHz frequency range

- 100 kHz real-time bandwidth

- Dynamic range

90 dB (FFT)

145 dB (swept-sine)

- Low-distortion (-80 dBc) source

- Up to 32 Mbyte memory

- GPIB and RS-232 interfaces

#### FFT analyzers starting at \$4950

The SR785 Dynamic Signal Analyzer offers state-of-art performance at a fraction of the cost of competitive analyzers. Standard features include swept-sine mode, order tracking, octave analysis, curve fit/synthesis, and arbitrary waveform source.

When compared to the Agilent 35670A, the SR785 comes out on top. It offers twice the frequency range (2 ch.) and 10 times the real-time bandwidth at less than half the price of the 35670A.

The SR785 is ideal for filter design, control systems analysis, noise measurement, audio or acoustical test, and mechanical systems analysis.

Take a close look at the SR785.

**Stanford Research Systems** 1290-D Reamwood Ave., Sunnyvale, CA 94089 • e-mail: info@thinkSRS.com Phone (408) 744-9040 • Fax (408) 744-9049 • www.thinkSRS.com

# pulse

# Device enables remote computer control and management

T support for computers in remote locations, which include areas as diverse as test equipment, desktop applications, and shoppingcenter kiosks, often requires the ability to take control of the application's computer over the Internet while maintaining a secure environment. Addressing that requirement, Lantronix has introduced its

IPv6 (Internet Protocol Version 6)-certified SpiderDuo KVM (keyboard/video/mouse)over-IP product. The device provides secure, real-time control of GUI (graphical-userinterface)-based computers, allowing authorized users to perform file transfers, system upgrades, and other tasks and the local port to control local tasks through the computer's keyboard, video, and mouse.

An optional power-control unit provides the ability to remotely control the power to the attached PC, allowing authorized users to initiate system reboots over the network. The power-control unit can put the PC in sleep or power-down mode to save energy, a feature not available with software-only controlling devices. SpiderDuo sells for \$380.

-by Margery Conner **Lantronix**, www.lantronix. com.

11.12.09

#### AVNET RELEASES XILINX SPARTAN-6 FPGA EVALUATION AND DEVELOPMENT KITS

The Avnet Electronics Marketing operating group of Avnet Inc has announced the Xilinx (www.xilinx.com) Spartan-6 LX16 FPGA evaluation kit and Spartan-6

The Spartan-6 LX150T development kit

targets video, industrial-networking and

(Peripheral Component Interconnect

LX150T FPGA development kit. Both kits support the new FMC (FPGAmezzanine-card)-expansion standard, which enables the addition of add-on modules and customization when working with FPGAs.

Avnet based the Spartan-6 LX16 evaluation kit on the Spartan-6 LX16 FPGA. It showcases a system-level approach to low-power design for the Spartan-6 family. Targeting use as a general-purpose FPGA development board, the kit is also suitable for portable instrumentation and battery-powered applications. To emphasize low-power applications, the kit receives its power from an included lithium-ion battery. It can also use a USB (Universal Serial Bus)cable connection or a 12V adapter and has six high-efficiency portablepower-management ICs from Texas Instruments (www.ti.com), A new **PSoC** (programmable system on

chip) 3 from Cypress (www.cypress. com) adds 20-bit precision analog, system-power management, USB/ UART/SPI (serial-peripheral-interface) connectivity, LCD direct drive, CapSense touch sensing, and FPGAconfiguration support. The \$225 board provides a low-pin-count FMCexpansion connector for adding FMC daughtercards. Avnet plans to begin shipping the kit by year-end. Xilinx will offer a \$295-base-price version that emphasizes flexibility.

Employing the Spartan-6 LX150T FPGA with its on-chip 2.5-Gbps transceivers, the kit provides a platform for developing low-cost, high-speed systems. The board features DDR3 memory, a 10/100/1000-GbE (gigabit-Ethernet) interface, and two low-pincount FMC-expansion connectors; it sells for \$995. For more, go to www. edn.com/091112pa.-by Rick Nelson

Avnet, www.em.avnet.com.

prototyping applications.

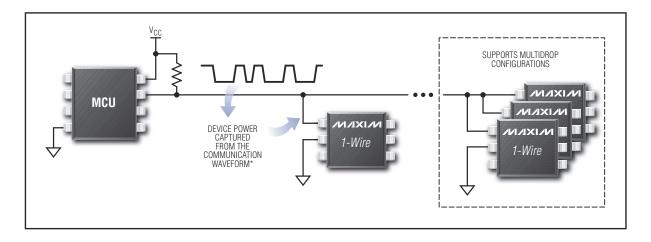

# **1-Wire<sup>®</sup> Advantage** Identify, Authenticate, Locate, and Protect *with 1 Pin*

#### **Customer's Concern**

Needs to add or control electronic functionality over a pin-limited connector or processor interface, potentially with a strong ESD performance requirement.

#### **Maxim's Solution**

1-Wire devices enable designers to add memory, security, control, and other mixed-signal functions over a single contact, easily and efficiently. ESD performance typically exceeds ±8kV Human Body Model.

#### **How It Works**

The 1-Wire bus is a simple signaling scheme that performs serial communication between a host/master controller and one or more 1-Wire slaves sharing a common data line. Both power and data communication for slave devices are transmitted over the single-contact 1-Wire line.

#### **Optimized for Your Application's Requirements**

- Unique, Factory-Programmed, Electronic Serial Numbers for Tracking or Security Functions

- NV Memory for Calibration, Use Tracking, Settings, or Manufacturing Data

- Crypto-Strong Authentication Enables

- License Management

- Protection Against NV Data Modification

- Bidirectional Host-Peripheral Authentication, Possibly over a Network

- Clone Prevention

- Single or Multipoint Temperature Sensing with Minimal Wiring Complexity/Cost

- I/O Sensing and Control

- Operation over Pin-Limited Connectors or with I/O-Limited MCU

1-Wire is a registered trademark of Maxim Integrated Products, Inc.

\*1-Wire devices with special features may require an additional power source.

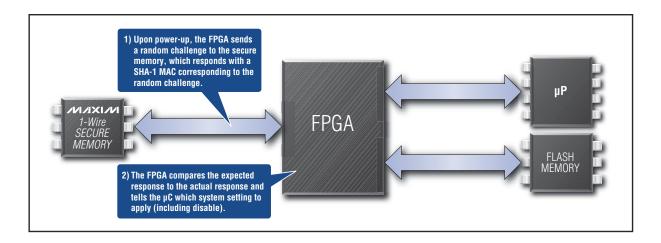

#### **Customer's Concern**

Need to securely and cost-effectively protect an FPGA design against unauthorized copying.

#### **Maxim's Solution**

Crypto-strong 1-Wire secure memories provide the FPGA design with a proven mechanism to self-test for validity.

#### **How It Works**

1-Wire memories utilize a FIPS 180-3 (ISO/IEC 10118-3) Secure Hash Algorithm (SHA-1) to implement a challenge-and-response authentication solution based on a private key. The success or failure of the FPGA authentication sequence is used by the system to set operation or action.

#### **Reference Designs**

Easy-to-use reference designs utilizing this cost-optimized copy protection scheme are available by the leading FPGA manufacturers. Visit **www.maxim-ic.com/fpga** for more information.

#### A Sampling of Innovative 1-Wire Solutions

| 1-Wire Product Family Function | Customer-Favorite Maxim Device                |

|--------------------------------|-----------------------------------------------|

| EEPROM                         | DS2431: 1Kb EEPROM                            |

| Crypto-secure authentication   | DS28E01-100: SHA-1 authenticated EEPROM       |

| Temperature measurement        | DS28EA00: ±0.5°C accurate digital temp sensor |

| OTP EPROM                      | DS2502: 1Kb EPROM                             |

| General-purpose I/O            | DS2413: 2-channel switch with 28V/20mA GPIO   |

| Unique, 64-bit serial number   | DS2401: 64-bit ROM serial number              |

| Real-time clock                | DS2417: 32-bit RTC counter                    |

#### www.maxim-ic.com/1-pin

www.maxim-ic.com/shop www

www.em.avnet.com/maxim

For free samples or technical support, visit our website.

Innovation Delivered is a trademark and Maxim is a registered trademark of Maxim Integrated Products, Inc. @ 2009 Maxim Integrated Products, Inc. All rights reserved.

# pulse

#### RESEARCH UPDATE

BY RON WILSON

### Team hardens SiGe circuits

anufacturers once aimed certain process technologies at radiation-hardened designs. CMOS, for example, started out that way, when RCA (www.rca. com) developed its silicon-onsapphire process. However, the overwhelming success of bulksilicon CMOS processes has driven most of the alternatives into niches, forcing up their cost to the point that only the bestfunded programs can use an alternative process technology to harden their circuitry. That situation leaves everyone else with plain-vanilla CMOS.

As a result, a lot of work over the years has taken place in hardening bulk CMOS. Several foundries offer radiationresistant processes that, by manipulating the device geometry, reduce the amount of charge that a radiated particle releases as it passes through an IC. Alternatively, these processes could increase the rate of recombination to mop up the charge before it can upset a logic node. In another method, designers use more resistant circuit-design techniques to help reduce either the probability of an upset or its consequences. These measures can take you only so far, however. Circuits that must operate in deep-space conditions, in which they will encounter not only ordinary ionizing radiation but also cosmic rays, also must rely on shielding and redundancy. Both techniques are costly in total mission weight.

Now, John Cressler, a professor at the Georgia Institute of Technology's School of Electrical and Computer Engineering, is leading a team exploring the traditional approach: hardening the process so that the circuits can survive radiation exposure without extensive shielding or redundancy. Cressler's team chose SiGe (silicon germanium) because of its ability John Cressler holds a SiGe IC wafer with nanoengineered circuits for use in a space environment.

to endure exposure to heavy, high-energy particles in cosmic rays. The team first built computer models of the response of SiGe devices to the passage of an ionizing particle through them. The team now intends to use an extremely high-speed oscilloscope to observe the picosecond-level electrical traces of particle impacts and to calibrate the computer models from the hard data. Cressler hopes to then refine device designs to produce a library of SiGe devices that can operate in space conditions without additional process hardening or shielding.

**Georgia Institute of Technology**, www.ece. gatech.edu.

# Digital photomultipliers challenge vacuum-tube photomultipliers

Despite massive improvements in solid-state light sensors in recent years, the detection of extremely low light levels has remained stubbornly resistant to the incursion of solid-state devices. The problems have been how to deal with the excessive dark count once you integrate the photodiodes into a circuit and how to reduce the cost of the specialized processes that the diodes require. In a paper from last month's IEEE Nuclear Science Symposium and Medical Imaging Conference (www. nss-mic.org/2009/NSSMain.asp), researchers from Philips Electronics claimed to have solved both problems.

Whenever a photon strike or a tunneling or thermal-energy event generates an electron-hole pair, the resulting tiny current pulse goes directly to a high-sensitivity inverter and becomes a digital signal for a counter. The Philips team puts an inverter on each diode and reduces the dark count by disabling any diode/inverter pair that shows excess pulses. An additional circuit on each pair quenches the avalanche photodiode after it has detected a photon and then precharges it to increase its sensitivity for the next arrival, substantially reducing operating power. Philips also integrates the diode, which requires a reverse-bias voltage of approximately 30V, with a low-voltage CMOS process.

>Philips, www.research.philips.com.

This apparatus provides the proof-of-concept test setup for a digital silicon photomultiplier.

SIGNAL INTEGRITY

#### BY HOWARD JOHNSON, PhD

### Shaping edges

igh-speed digital simulations usually begin with a timedomain specification of the driving signal. The specification calls out every moment at which the driving signal, or "excitation," should transition. From that data, the simulation then builds a time-domain sequence or subroutine depicting the excitation as a function of time. As the simulation proceeds, it applies edge shaping to each signal transition.

You can think of the edge-shaping process as a linear filtering operation. For example, pass a perfectly squareedged time-domain signal through a Gaussian lowpass filter, and it produces—guess what—Gaussian edges. Each signal edge looks like the integrated form of a Gaussian bell-shaped curve. You may recognize that shape from statistics as the Gaussian error function, erfc(). Set the Gaussian lowpass filter's -3-dB bandwidth to 0.361/*T*, and it will form signal edges with a 10 to 90% rise and fall time of precisely *T*. This discussion assumes that you have sufficiently separated the signal-transition points to produce a clear and complete copy of the signal edge's shape at every transition.

If you tear apart your simulator code, you may never find an explicit linear signal-filtering routine. There are many ways to make properly shaped signal edges, but they are each equivalent to some linear filtering operation. In every case, the simulator endows the signal with a frequency-response characteristic of the equivalent lowpass fil-

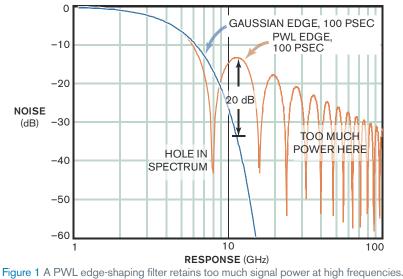

ter you used to create the signal edges. Figure 1 plots the frequency response of two popular edge-shaping filters. The 10 to 90% rise and fall time of each filter is 100 psec. The Gaussian filter exhibits a smooth frequency response with little signal power above 10 GHz. The PWL (piecewise-linear) filter retains an unrealistically large amount of signal power above 10 GHz. This situation happens when you use a PWL function in Spice to create a single linear ramp at each signal edge. Such signals look good on a timing diagram, but they do not represent the spectral qualities of your system.

The PWL filter has a rectangular, or "boxcar," impulse response. When you play a digital signal through a boxcar filter, it creates steps with linear rising and falling edges. If the 10 to 90% rise time is T, then the 0=100% rise time must be 1.25T. That figure is the actual width of the filter's boxcar response, which accounts for its spectral null at 8 GHz. The sharp corners at the beginning and end of each PWL edge account for the extra signal power at very high frequencies. At 12 GHz, the PWL spectrum peaks some 20 dB higher than the Gaussian spectrum.

I avoid PWL simulation because the PWL edge exaggerates by an order of magnitude the importance of system artifacts around 12 GHz. The PWL edge masks artifacts at 8 GHz because there is no signal energy at 8 GHz to test for such defects. It also vastly overstates crosstalk at high frequencies.

Whenever you need to see details of your actual signal edge shape or spectrum, use a signal-shaping process that properly represents the signals at hand. If you have a record of the actual signal shape or can extract it from an IBIS (input/output-buffer-information) file, use it. In the absence of other information, use a Gaussian shape.EDN

Howard Johnson, PhD, of Signal Consulting, frequently conducts technical workshops for digital engineers. Visit his Web site at www.sigcon.com. SERDES-Capable FPGA Solutions for Wireless and Wireline Applications

### LET LOW POWER GUIDE YOUR WAY. INTRODUCING THE ECP3<sup>™</sup>. THE LOWEST-POWER

SERDES-CAPABLE FPGA IN THE INDUSTRY.

Built for high-speed communications protocols, the ECP3 helps you keep your power budget down, and applications features high. At half the power and half the price of competitive devices, now you can do more with less.

Learn more about the ECP3 family at: latticesemi.com/ecp3

IN PRODUCTION

TAPEOUT

#### BY PALLAB CHATTERJEE, CONTRIBUTING TECHNICAL EDITOR

# Reference-tool flows and process-design kits, part two

n design support for the fabless or foundry-based semiconductordesign model, the main mechanism for circuit-design information is the PDK (process-design kit). The PDK describes the electrical, yield, and performance aspects of the process. There are generally two types of PDKs: one for device-level or custom design and one for logic-level design. The device-level PDK typically comprises Spicelevel device models for all of the active devices available on the process; Spice-level device models for all of the designable passive elements, including resistors, capacitors, and inductors; a schematic-symbol library

for these primitive elements; and information on how to build the device in layout.

The Spice models are fairly universal in the semiconductor industry and useful with a variety of simulators, including those for IR (current/resistance) drop; electromigration analysis; postlayout-extraction, high-capacity, mixed-mode simulators such as VHDL-AMS (very-high-speed-integrated-circuit hardware-description-languageanalog/mixed-signal) and Verilog-AMS; ac or harmonic-balance RF simulators; and cell-characterization simulators. Spice-level subcircuit models are available for some processes that involve complex elements, such as highvoltage or high-current transistors and metal-insulator-metal capacitors.

The second design view for the custom-design level is for the physical design. It includes the layer list and the technology file for the layout editor and generally references either layouts of the devices to show how to construct a device or an automated program to build the devices from parameterized cells in the language

#### It is no longer always accurate to assume that experienced designers will be working with PDKs.

of the layout editor. These parameterized cells are for individual devices, device pairs, and other configurations that the process supports and are available for both passive and active components.

The parameterized cells tend to be version-specific for a given layout editor and are generally in the design database as "generate-as-needed" elements. Using parameterized cells maintains design flexibility but involves a revision-control risk for the context around the dynamic device. It is common that PDKs omit the reference layouts and parameterized cells for the layouts' nondevice objects, such as guard rings, substrate and well taps, dummy devices, polysilicon or diffusion interconnect, via and contact farms, field plates, line shields, and high-current or high-voltage corner designs.

The next level in the design includes the logic-level PDK. This PDK comprises descriptions for how to set up place-and-route tools, block-toblock-assembly rules, maximum-device-size rules for buffers and repeaters that insert automatically in a design, some schematic symbols for primitive logic elements, and I/Os. The I/Os tend to be special cells that incorporate ESD (electrostatic-discharge)protection devices, which are processspecific elements. Information for designing these ESD elements is generally proprietary to the foundry. The I/O cells also contain the core and peripheral power-interface circuits. The PDK not only provides these cells but also identifies the proper use and density of the cells a design requires.

First-generation PDKs assumed that a designer using the kits had sufficient design experience and knowledge to properly apply the design information over multiple applications. As a result of the shift to global design centers and the reduction in time designers spend on each process node, it is no longer always accurate to assume that experienced designers will be working with these kits. A proposed method of addressing this issue is to shift to the Python programming language (www. python.com) and the use of that language's multidevice PyCells.

The PyCell device builders include the advantages of adjacent partner devices and their associated nondevice elements. Less-experienced designers may use PyCells with an automated placer to build the device-level IP (intellectual property) and associated cells without requiring the help of senior designers for anything but cell sign-off.EDN

Contact me at pallabc@siliconmap.net.

+ www.edn.com/tapeout

# Show your team how it's done

#### Jump ahead with CST STUDIO SUITE™.

#### CST technology for SI/PI and EMC/EMI analysis.

→ Get equipped with leading edge 3D EM technology. CST's tools enable you to characterize, design and optimize electromagnetic devices all before going into the lab or measurement chamber. This can help save substantial costs especially for new or cutting edge products, and also reduce design risk and improve overall performance and profitability.

Involved in SI/PI analysis? You can read about how CST technology was used to simulate and optimize a digital multilayer PCB's performance at www. ightarrow Grab the latest in simulation technology. cst.com/pcb. If you're more interested in EMC/EMI or microwave components, we've a wide range of worked application examples live on our website at www.cst.com/apps

CST's flagship product, CST MICROWAVE STUDIO® [CST MWS], is the market leading time domain tool

for 3D EM simulation. Embedded in an advanced design environment, CST MWS can be coupled with all CST STUDIO SUITE™ solver technology including PCB. circuit and thermal simulation.

Now even more choice for SI/PI simulation

- CST PCB STUDIO<sup>™</sup>

- CST CABLE STUDIO<sup>™</sup>

- CST MICROWAVE STUDIO<sup>®</sup>

Choose the accuracy and speed offered by CST STUDIO SUITE™.

CHANGING THE STANDARDS

# The path of least resistance

nananananan Ti Ti Ti Ti Ti

CONTACT

TRANSMISSION

www.samtec.com/tls

#### High Speed Edge Card

- Rugged Edge Rate<sup>™</sup> contact system on .8mm pitch is robust when zippered during mating and unmating

- Rated at 10.5 GHz in differential pairs

- Vertical, right angle, horizontal designs

#### Razor Beam™ System

- Ultra fine pitch interconnects on .4mm, .5mm, .635mm pitch

- Minimizes board real estate connector pitch (length) and width

- Low profile down to 4mm board spacing

- Rated at 10 GHz in differential pairs

#### Tiger Eye™

**NE SOLUTIONS**

- High reliability, three finger BeCu Tiger Eye<sup>™</sup> contacts

- .8mm pitch, 6 to 10mm stack heights

- Shrouded, polarized, optional locking clips and weld tabs

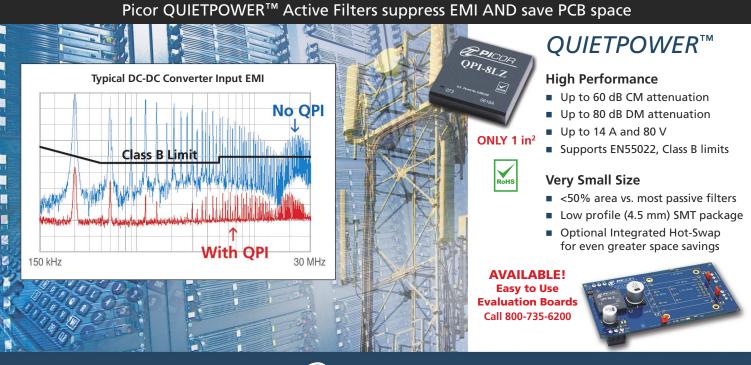

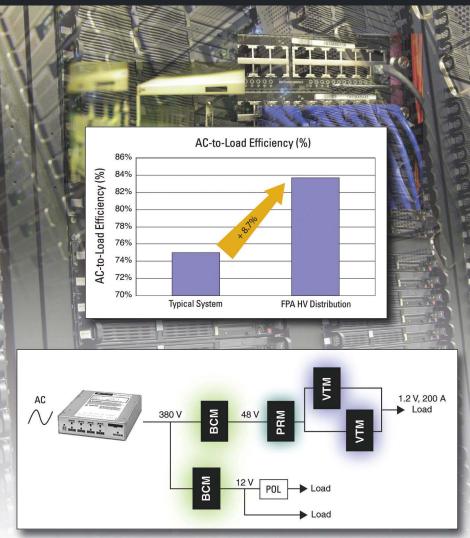

# INDUSTRY STANDARDS LEAD PUSH TOWARD ENERGY-EFFICIENT COMPUTING

NOWATTHON

ENVIRONMENTAL CONCERNS AND RISING ENERGY COSTS ARE SPURRING INDUSTRY AND GOVERNMENT GROUPS TO DEVELOP REQUIREMENTS FOR HIGH-EFFICIENCY AC AND DC POWER CONVERSION, LEADING TO ENERGY-EFFICIENT SERVERS. MEETING THE NEWEST SPECIFICATIONS WILL DEMAND KNOWL-EDGE OF COMPETING POWER-CONVERSION TOPOLOGIES, COMPONENTS, AND DESIGN.

#### BY LEE HARRISON • PERITUS POWER

n addition to environmental concerns, the increasing cost of electricity is driving data-center managers to more energy-efficient installations. As utility bills become the primary expense for data centers, electricity costs now outweigh real-estate costs, with power consumption per data center ranging from 2 to 22 MW. In 2007, the Internet accounted for 9.4% of total US electricity consumption and 5.3% of global electricity consumption. Networking equipment, such as modems, routers, hubs, and switches, accounted for about 25% of the electricity demand in an average office. If the computers and servers in an infrastructure require 200 kW, then the networking components in that infrastructure

need 50 kW. In addition, 45% of the power a data center consumes is for airconditioning and cooling. In modern data centers, performance per watt has become more critical than performance per processor.

Every year, computers and servers demand higher performance. Server and PC manufacturers respond with larger and faster disk drives, faster memory, multicore processors, and more I/O devices. Although this approach satisfies customer demand, the new designs often require more power and additional cooling, continuing the trend toward higher power consumption. The average power consumption per server has increased from 150 to 250W in 2000 to 450 to 800W in 2009, and the average power per rack of servers in 2000 was nearly 1 kW, rising to 6 to 8 kW in 2006, and should top 20 kW in 2010.

Environmental concerns are not the only ones behind the push to energy efficiency. Electronic equipment that runs cooler has lower failure rates and increased reliability. Data centers save money when servers require less power because less power means decreased cooling and air-conditioning costs. Large data farms benefit from relatively small reductions in electricity cost. Google, for example, may be able to save nearly \$1 million a year in utility bills by reducing power consumption by 2 to 3%. Some industry analysts believe that financial benefits are more important than climate issues; in a time of reducing costs across all businesses, this belief may be one factor in the drive toward energy efficiency.

The ac/dc power-conversion step in the overall power chain for server farms can yield some of the most significant gains in power efficiency. Many industry and government groups, including 80 Plus, EPRI (Electric Power Research Institute), the CSCI (Climate Savers Computing Initiative), and the US Environmental Protection Agency, have

developed requirements for high-efficiency ac/dc power supplies. Table 1 shows the current targets that the CSCI and Energy Star define for single-output power supplies. Table 2 shows multipleoutput supplies (Reference 1).

The Silver category is challenging for some power vendors, but the Gold and next-generation Platinum levels are more difficult to reach. Some powersupply vendors have achieved the Gold standard, and some servers are currently available with Gold power supplies, but the Gold standard is unlikely to become well-established until the end of 2010. To meet those standards, manufacturers have taken different approaches, including using interleaved PFC (power-factor control), bridgeless PFC, and resonant topologies.

#### **INTERLEAVED PFC**

The power industry has long used interleaving techniques in multiphasebuck-converter designs. This design commonly meets fast load-transient demands for DSPs and other processors. Some designs interleave multiple synchronous power stages to increase power delivery to the load and decrease input and output capacitance, maximizing the benefits of smaller output inductors in each phase of the design. Due to the ripple-current cancellation effects at the output capacitors, this topology can realize transient demands in excess of 350A/µsec.

Interleaving PFC boost stages benefits from the same principles. PFC boost encompasses CCM (continuous conduction mode), DCM (discontinuous conduction mode), and CRM (critical conduction mode). High-efficiency designs are likely to use CCM in the server area because this mode of operation suits power supplies with more than 350W of output power. Although CCM eases the design of EMI (electromagnetic-interference) filters, the approach generally requires a larger boost inductor than do alternative design techniques.

#### AT A GLANCE

The ac/dc power-conversion step in the overall power chain for server farms can yield some of the most significant gains in power efficiency.

To meet industry standards, manufacturers have taken different approaches, including using interleaved PFC (power-factor control), bridgeless PFC, and resonant topologies.

Thanks to its 0V switching losses, higher switching frequencies, and smaller footprints, resonant-converter topology may be able to achieve Energy Star Platinum standards.

Solution For the near future, silicon will remain the dominant switching semiconductor material, and gallium nitride will start to make inroads over the next year.

Interleaved CCM is not without its own risks: The design suffers from inherently higher switching and reverserecovery losses in the rectifier. You can partially overcome these losses, however, by using silicon-carbide diodes. In addition, you cannot typically adjust the frequency in CCM designs because CCM operates as an average-currentmode, PWM (pulse-width-modulated)control, fixed-frequency design, forcing average input current to be proportional to the rectified ac line cycle.

Energy Star specifications are the primary reason for the move to interleaved PFC. As enclosures and footprints for power become smaller, however, the better EMI performance helps reduce the size of EMI filters. Power density is excellent for interleaved PFC designs, but circuit design can be difficult; the design challenges include its many modes of operation, the need to guarantee safe operation at start-up and shutdown, autoranging of wide-input sources, and fault conditions.

To achieve high efficiency at loads less than 15%, particularly around the 5 to

10% range, you will likely need some form of phase shedding, pulse skipping, or burst modes. These approaches can be fully autonomous or selectable through software and DSPs, depending on load. No matter which approach you choose, problems arise because other functions can be occurring simultaneously. Although using pulse skipping and burst modes lets you attain increased efficiency at light loads, they wreak havoc when you are trying to accurately measure PFC, and they can cause EMI issues and strange harmonic effects in racks and across servers that connect to the same ac source supply.

Measuring PFC at light loads requires the use of a line-impedance-stabilization network and a capacitor between the ac source and the power supply. Investigations are ongoing that aim to reveal the effects of measuring PFC under these conditions. Determining the reason for strange harmonic effects in high-efficiency power conversion also requires further investigation. Thus, efficiency comes at a price. You may be able to improve efficiency, but doing so introduces new side effects.

Implementing PFC in burst or skipping modes also causes problems for the digital-sensing input-voltage, -power, and -current outputs. Although fully digitally controlled power supplies can likely cope with these problems, it's difficult to obtain valid data from a control signal that is constantly changing. Many designs turn off power reporting at these lighter load conditions, but Energy Star is determined to tighten the already difficultto-meet specifications, so designers must find approaches for reporting data at light loads. Digital techniques in PFC have recently produced impressive performance at light loads but at the expense of THD (total harmonic distortion).

#### **BRIDGELESS PFC**

Bridgeless PFC offers loss savings of 0.4 to 1.5W at high-load conditions,

| TABLE 1 TARGETS FOR SINGLE-OUTPUT POWER SUPPLIES |                                       |                     |                     |                                     |                     |                     |                   |                       |                       |

|--------------------------------------------------|---------------------------------------|---------------------|---------------------|-------------------------------------|---------------------|---------------------|-------------------|-----------------------|-----------------------|

|                                                  | CSCI Silver and Energy Star Version 1 |                     |                     | CSCI Gold and Energy Star Version 1 |                     |                     | CSCI Platinum     |                       |                       |

| Loading<br>(%)                                   | Efficiency<br>(%)                     | <b>PFC</b> (≤1000W) | <b>PFC</b> (>1000W) | Efficiency<br>(%)                   | <b>PFC</b> (≤1000W) | <b>PFC</b> (>1000W) | Efficiency<br>(%) | <b>PF</b><br>(≤1000W) | <b>PF</b><br>(>1000W) |

| 10                                               | 75                                    | 0.65                | 0.8                 | 80                                  | 0.65                | 0.8                 | 82                | 0.65                  | 0.8                   |

| 20                                               | 85                                    | 0.8                 | 0                   | 88                                  | 0.8                 | 0.9                 | 90                | 0.8                   | 0.9                   |

| 50                                               | 89                                    | 0.9                 | 0.9                 | 92                                  | 0.9                 | 0.9                 | 94                | 0.9                   | 0.9                   |

| 100                                              | 85                                    | 0.95                | 0.95                | 88                                  | 0.95                | 0.95                | 91                | 0.95                  | 0.95                  |

| TABLE 2 TARGETS FOR MULTIPLE-OUTPUT POWER SUPPLIES |                |      |                |      |                |      |  |  |

|----------------------------------------------------|----------------|------|----------------|------|----------------|------|--|--|

|                                                    | CSCI Bronze    |      | CSCI Silver    |      | CSCI Gold      |      |  |  |

| Loading (%)                                        | Efficiency (%) | PFC  | Efficiency (%) | PFC  | Efficiency (%) | PFC  |  |  |

| 20                                                 | 82             | 0.8  | 85             | 0.8  | 87             | 0.8  |  |  |

| 50                                                 | 85             | 0.9  | 88             | 0.9  | 90             | 0.9  |  |  |

| 100                                                | 82             | 0.95 | 85             | 0.95 | 87             | 0.95 |  |  |

depending on output power. The benefits of a low-power-line mode are much greater and suit countries that still run servers in low line conditions. Standard bridge rectifiers suffer in this application because they use series-connected semiconductors, but the approach remains a low-cost and reliable choice for ac rectification. In some designs, standard bridge rectifiers run at dangerously high temperatures. Airflow is typically not ideal in the location of a 1U server power supply, and some customers of power-semiconductor manufacturers have requested an increase in thermal capabilities to 175°C from the previous limit of 150°C.

Bridgeless approaches have not become mainstream designs due to their higher cost and challenges, including complex gate-drive circuits and the difference between the input and the output ground references. Prototypes of bridgeless designs have shown high-EMI common-mode switching elements at the negative bulk-capacitor connection, and, with virtually no low-frequency path back to the ac source, EMI is greater. Various semiconductor companies, including STMicroelectronics and On Semiconductor, now offer controllers for bridgeless rectification, although some operate only in high line conditions. These units operate at fixed frequencies of approximately 100 to 150 kHz, but the \$20 to \$60 cost to implement bridgeless front ends is too high for a 1W power saving.

For now, CCM designs with carefully used silicon and light-load power-saving techniques have sidelined bridgeless designs. Unless there is a major breakthrough in the cost, complexity, and confidence of bridgeless technology, this scenario may remain so for some time to come. In addition, if dc-based power-distribution infrastructures for data farms become popular, ac/dc bridgeless technology may become obsolete before it gets off the ground.

#### **RESONANT TOPOLOGIES**

Thanks to its OV switching losses, higher switching frequencies, and smaller footprints, resonant-converter topology may be able to achieve Energy Star Platinum standards. Moreover, parasitics, which are problematic for alternative topologies, become advantageous in resonant topologies (Table 3). PWM designs lose power at high switching frequency, and resonant-mode topology begins where PWM topologies end. There are many options available in waveform shaping to eliminate switching losses, including ZCS (zero-current switching); ZVS (zero-voltage switching); and quasiresonance, which uses only a part of the sinusoidal waveform.

Power designers commonly choose

| TABLE 3 COMPARISON OF RESONANT POWER SUPPLIES            |                                                                                                                                                                                           |                                                                                                                                                                                                                                        |  |  |  |  |  |

|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Converter                                                | Advantages                                                                                                                                                                                | Disadvantages                                                                                                                                                                                                                          |  |  |  |  |  |

| Series resonant                                          | Behaves as a current source and best suited to<br>high-voltage, high-power designs<br>Provides good handling of overload and fault<br>conditions<br>Requires small or no output filter    | Poor regulation at light- and no-load conditions<br>Continuous-current mode below resonance causes<br>high component stress and premature failure if not<br>carefully designed                                                         |  |  |  |  |  |

| Parallel resonant                                        | Behaves as a voltage source and suitable for low-<br>voltage outputs, good no- and light-load regulation<br>Discontinuous mode of operation is similar to<br>standard PWM buck conversion | Requires snubbers, consuming efficiency<br>Does not self-protect in overload or short-circuit con-<br>ditions, requiring additional protection<br>Constant resonant circulating current at all load condi-<br>tions can cause problems |  |  |  |  |  |

| Zero-current switching, quasiresonant, fixed on-time     | Low turn-off losses in silicon<br>Recycles any remaining leakage current                                                                                                                  | Power components contain high peak currents                                                                                                                                                                                            |  |  |  |  |  |

| Zero-voltage switching,<br>quasiresonant, fixed off-time | Virtually eliminates switching losses<br>Recycles any remaining leakage current                                                                                                           | Operates above resonant range<br>Power devices require at least three times the supply<br>voltage; multiresonant techniques offset this problem                                                                                        |  |  |  |  |  |

| Series-parallel resonant                                 | Excellent performance at light-load, no-load, and short-circuit or fault conditions                                                                                                       | Produces parasitic elements that can be troublesome, requiring additional passive components                                                                                                                                           |  |  |  |  |  |

| Multiresonant, zero-voltage-<br>switching Class E        | Virtually eliminates switching losses, virtually no frequency shift compared with other methods                                                                                           | Can cause stability issues and generates high peak voltage and current across semiconductors                                                                                                                                           |  |  |  |  |  |

| Clamped PWM                                              | Simple control loop with low-voltage stress<br>Current-mode capable and fixed frequency of<br>operation                                                                                   | Turn-on losses can be high; operates best at medium-<br>to full-load conditions                                                                                                                                                        |  |  |  |  |  |

| PWM, zero-voltage<br>switching                           | Fixed-frequency design with maintained switching<br>losses at low levels across all power devices<br>High efficiency at high switching frequency                                          | Creates problematic switching noise at light loads and<br>does not achieve zero-voltage switching in the light-<br>load mode of operation                                                                                              |  |  |  |  |  |

| LLC resonant                                             | High efficiency with excellent line/load regulation<br>Outperforms series-resonant mode                                                                                                   | Performance is superior to other modes of operation,<br>but design is critical<br>Possible N+1-redundancy concerns                                                                                                                     |  |  |  |  |  |

LLC (inductor-inductor-capacitor) converters to implement resonant topologies. These devices offer good regulation and frequency control, and they boast efficiency as great as 97% for the LLC stage, further assisting compliance with the Platinum standard. LLC topologies also have reduced inductance in the primary transformer, excellent frequency control over a wide load range, excellent line and load regulation down to zero loads, and ZCS control of secondary rectifiers.

#### **MATERIAL AND MAGNETICS**

For the near future, silicon will remain the dominant switching semiconductor material, and gallium nitride will start to make inroads over the next year (**Reference 2**). Gallium-nitride promises a tenfold reduction in on-resistance for 50V devices by 2013, but no more than 10% of applications will be widely implementing it before 2015. Using planar transformer technology and integrated magnetics with power components as part of the transformer assembly can achieve 0.5 to 2W savings. Planar magnetics offer lower switching and copper losses. They also offer a low profile, high power density, and high frequencies, so designers can build them into the main PCB (printed-circuit board) or assemble them as subassemblies for daughtercards.

Integrated magnetics can provide a 50% smaller footprint than you can achieve using separate magnetic and rectification stages. Thanks to lower commutation loops, the approach also offers lower, better-controlled high-frequency power-supply noise spikes and EMI, and reduced copper losses guarantee increased efficiency. Generally, integrated magnetic designs offer repeatability and cost reductions in manufacturing, and the tolerances of magnetic characteristics and output stages show closer results to each other than those of discrete stages. This technology will find its way into future high-efficiency designs; the option of increased power density alone is a big enough reason to adopt the technology. Efficiency gains may even become secondary to this requirement.